HOME >> 鉄道模型実験室 > バイナリカウンタの動作解析と対策

鉄道模型実験室 No.110 バイナリカウンタの動作を観察する

■ はじめに

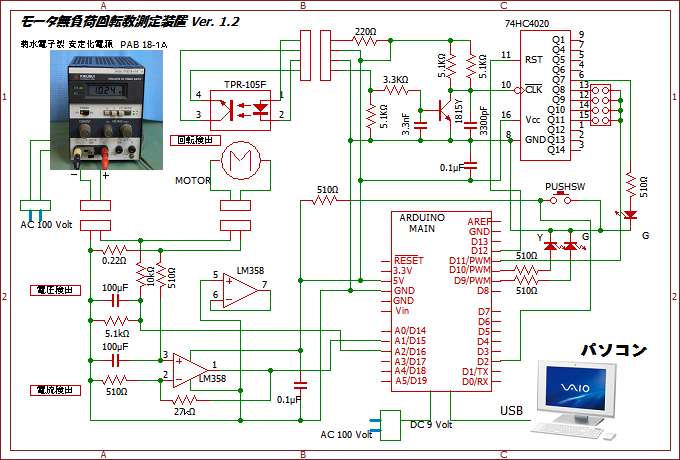

先回「バイナリカウンタの動作を観察する」で報告したように、新しく制作したモータ無負荷回転特性の測定用シールドの不可思議な現象について、読者の方からアドバイスを頂いた。 このような問題に対しての攻め方については五里霧中の小生にとって、貴重な指針となりました。 そして見事その対策が出来ましたので報告いたします。 アドバイスして下さった Mさんに改めてお礼申し上げます。

■ 問題点の整理

モータの無負荷回転特性の測定シールドでの問題は、

- 回転数のカウントが合わない。

- 入力信号のGNDレベルがドリフトしている。

の2点である。 第2点は結果に影響しないものの、現象が不明なのでこの装置の信頼性が疑われるのである。

Mさんのアドバイスによると、何らかの原因でカウンタが1クロックで、2クロック分カウントしている様です。 クロック波形のスレッショルド付近で小さなバタつきがあるのかもしれませんとの洞察を参考にして、原因追及を実施していくことにしました。

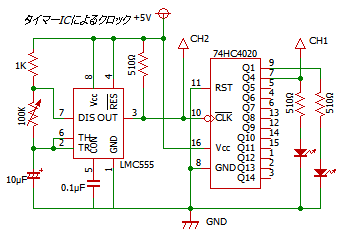

■実験1: タイマーICを使っての確認

まず、カウンタ自身の作動を確認しておくために、タイマーICを用いて正確なパルスを発生させ、動作状況を確認することにしました。 回路図と実験状態を下に示す。

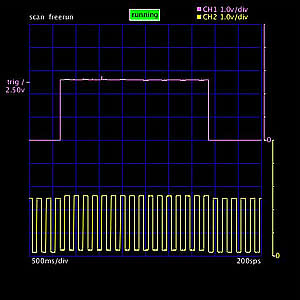

電源は、5Volt のACアダプタを使用し、オシロシールドに入力してパルス波形を観察しました。

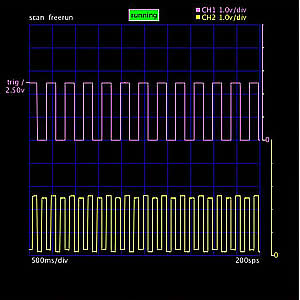

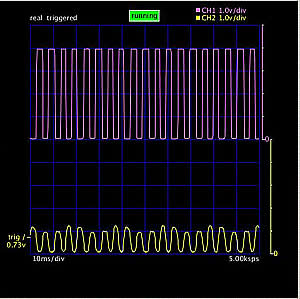

左から、CH1をQ1ポート、Q4ポート、Q5ポートに接続した状態です。 オシロシールドの入力は1/2のゲインに接続しています。 を5Hz程度のゆっくりとしたパルスですが、入力・出力共に綺麗なパルス波形となっています。 各ポートのカウント状態も異常ありません。 カウンタは正常に機能していることが確認できました。

しかし、よく見ると入力パルスのGNDが少しドリフトしているのが分かります。

■実験2: 作動確認用のLEDを切る

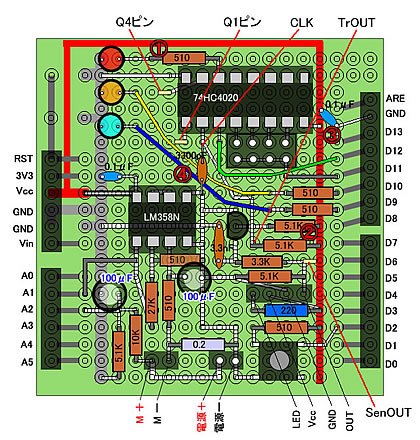

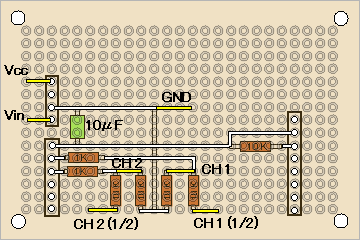

カウンタは正常に機能していることが確認出来たのでの、問題のシールドを使って実験を進める事にします。 先回、写真で説明しました、実際の回路の様子を説明するために、実体配線図のイラストを作って見ました。 裏表の配線があるのでゴチャゴチャとしていますが、どこがどのように配線したかが分かると思います。

画面をクリックすると原画である PNG形式のファイルが表示されますので、参考にしてください。

回路の修正などの手を加えて部分を丸数字を付与していますので下記の説明の参考にして下さい。 また、オシロ端子との接続のために、観察用の端子を設けています。 ここにクリップを挟んで波形を観察することにしています。

*************************************

では、アドバイスに従って、実験していった手順で説明して行きましょう。

最初は、入力パルスのGNDドリフト調査のために、カウンターICの負荷となっているLEDの作動を停止させて様子を見ることにしました。 まる1の部分の裏側のハンダを切ってLEDの作動を止めて観察しました。 動力ユニットのジャンク品(とは言ってもモータは作動します)に回転センサーを取り付けて、パルスを発生させて波形を観察することにしました。

.

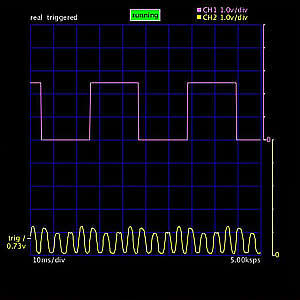

結果は上記のとおり、以前の状態のままで改善されていませんでした。 CH1はQ4ポートに、CH2はTrOUT(トランジスタの出力端子)に接続し、ゲインはそれぞれ1/2に接続しています。

.

.

しかし、ここである事に気が付きました。TrOUTをCH2の1/2ゲイン端子に接続すると上記の様ですが、1/1ゲイン端子に接続するとGNDのドリフト発生が止まるのです。 条件を変えて何度か観察してみましたが、様子は同じであり、原因はオシロシールドにあると推察しました。

■実験3: オシロシールドの修正

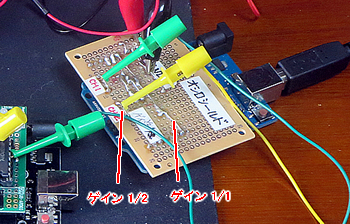

GNDのドリフトはこのオシロシールドが関係していると睨んで、改良することにした。 問題のオシロシールドを示す。

.

.

このシールドは「オシロ用のシールドを作る」にて制作したものですが、その後、ハイ・インピーダンス化として1MΩを使用してゲインを 1/3 から 1/2 に落とし、さらにゲイン1/1のフックを作るなど、改造しています。 このため、みっともない格好のハンダ付け状態となっています。 そして、リード線を接続するフック部分を含めて、CH1とCH2の配線が交差する状態となっています。 このため、お互いの信号路が接近して干渉しているのではないかと想定しました。

そこで、抵抗の位置を変えて、配線が交差しないように修正した。 さらに、1MΩの抵抗を 10KΩまで落として使うことにした。 これは、静電誘導を少しでも減らすために、多少は電流が流れる様に素人考えで実施したものです。 その理由の可否は自信ありません。

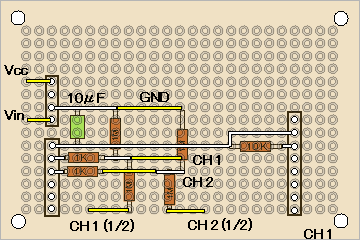

実体配線図を左に示す。 黄色の配線部分はクリップのためのフックを示しています。 完成したシールドを下に示す。

.

.

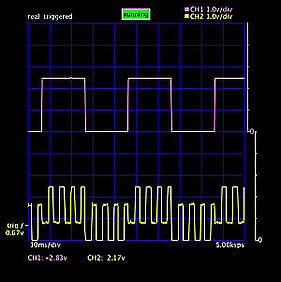

そして、実際に使用した場合のオシロ画面を右に示す。

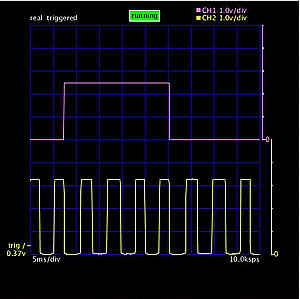

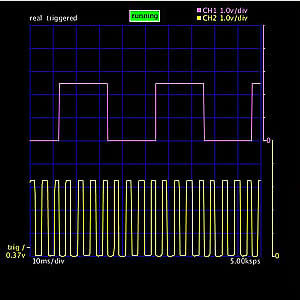

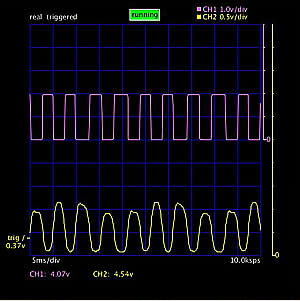

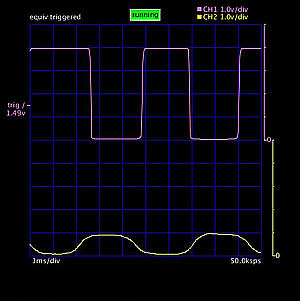

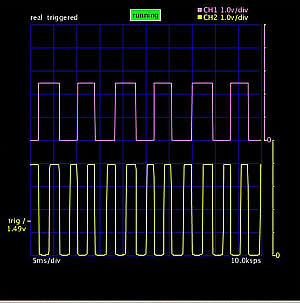

CH1はQ4ポートにゲイン1/2にて接続し、CH2はTrOUTポートにゲインは1/1で接続しています。 時間軸を5msと10msにて表示させたものです。

オシロ画面を見ると、入力パルスのGNDドリフトは発生していないので、この対策は正解だっと判断しています。

***********************************

そこで、カウンタの入力系の波形をいろいろ観察してみることにしました。

まず、TrOUT を CH1(1/2)に、SenOUT をCH2(1/1)に接続して波形を観察したものを下の左と中央に示す。 また、Q4ポートを CH1(1/2)に、、SenOUT をCH2(1/1)に接続した場合を右に示す。 ここで、かっこ内はゲインを示す。

まず、センサからの信号である SenOUT を見ると、4サイクル毎に変化していますが、これはモータのフライホイールに付けたマーキングが4か所あるため、1回転当たりに4回パルスが出ていることを示しています。 そして信号のGNDドリフトは発生していないことも分かります。

.

.

次に、プリアンプ部の出力である TrOUT の波形を見ると、丸っこい SenOUT の波形を綺麗な矩形波に変換していることが分かります。 そして、時間軸を拡大していっても、ダブルカウントに影響するような ヒゲらしき波形 は観察できませんでした。 時間軸拡大すると、このソフトの限界である50KHz のサンプリング周波数に影響すると思われる見慣れた波形が出現してしまうのです。

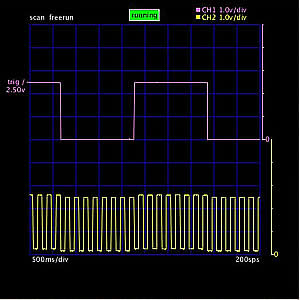

また、Q4ポートの波形(上右の CH1(1/2)に示す)の波形は、相変わらずカウント数が合いません。 そして、Q1 ポートも観察しましたが、反応がありません。 ズーと Low を示していました。

無駄と思いながら、カウンタのクロック入力端子の状態を観察したのが右の画面です。 CLKの信号をCH1(1/2)に、 TrOUT を CH2(1/1)に接続した状態です。 異常ないように思われますが、CLKの信号の High レベルが 3volt 程度である事に気が付きました。 プリアンプ部の出力である TrOUT の電圧が低いようです。

早速、カウンタのの説明書を開いてみました。 入力電圧の H レベルは、Vcc = 4.5v 時に min. 3.15v と明記されている。 ヤバイ! カウンタが進んでいるのでこの条件は満たしているとは思われますが、ギリギリなのか、あるいはノイズが乗りやすい状態なのかも知れません。

そこで、M さんのアドバイス、「CLKのTRの負荷抵抗を小さくしてみる」に従って、プルアップ抵抗を小さくしてみることにしました。

■実験4: プリアンプ部の抵抗を小さくする

目的は、プリアンプ部の出力電圧をアップさせることです。 当初からそうしておけばよかったのですが、なぜ 5.1KΩにしたのか思い出せません。 何かの回路を参考にしたものと思われます。 どの程度にすればよいのかはトランジスタの特性を考慮して計算すれば良いのですが詳しくないので、半分にしてみることにしました。 理由はこの 5.1KΩの抵抗の横が丁度開いていたので、並列に同じ抵抗を並べる事が出来たからです。 上記の説明図のまる2の部分です。

そしてまる3のパスコンをカウンタIC の傍にも追加して、ノイズ対策を実施しました。

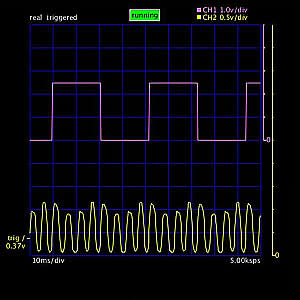

TrOUT を CH1 (1/1) に、SenOUT をCH2 (1/1) に接続して波形を観察したものを上の左と中央に示す。 右の画面は、Q4ポートを CH1 (1/2) に、、SenOUT をCH2 (1/1) に接続した場合を示す。 プリアンプ部の出力電圧(TrOUT)を 4volt までアップさせる事が出来ていますが、Q4ポートの出力は、相変わらず4パルス毎にカウントしています。

■実験5: コンデンサの追加

そして、次の 「CLK端子近くに数100PF程度のコンデンサーを入れてみる」 と言うアドバイスを実行することにしました。 クロック波形のスレッショルド付近で小さなバタつきを防止するためのコンデンサと解釈しました。 ただし、101、すなわち100pF のコンデンサの手持ちが無かったので 332K、すなわち3300pF のコンデンサを使ってみました。 挿入場所は、上記の説明図のまる4 の部分で、CLK 端子と GND の間に挿入しました。

.

.

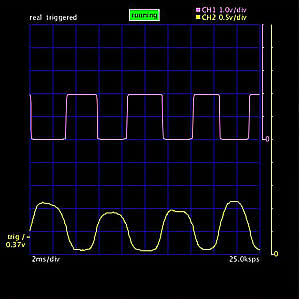

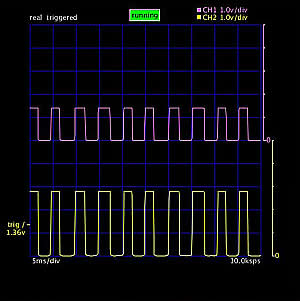

CLKの信号をCH1 (1/1) に、 SenOUT を CH2 (1/1) に接続した状態を上左に示す。 コンデンサによる波形のダレはほとんど無いと言えるでしょう。 そして CH1 (1/2) をQ4ポートに変えた状態を中央に示す。

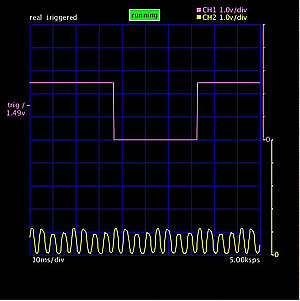

思わず、出来たぞ! と叫びたくな様な波形ですね。 Q4ポートは確かに8パルス毎に変化しています。 そして、 CH2 (1/1) を TrOUT に変えた状態を上右に示す。 うれしい波形ですね。

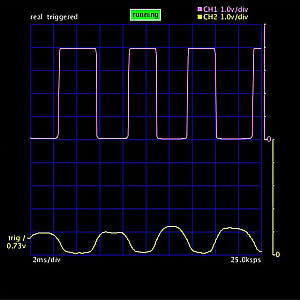

そして、試しに CH1 (1/2) をQ1ポートに変えた状態を右に示す。 今までダンマリだったQ1ポートが生き返ったように活動しているのが分かります。

■ 結論

以上の実験結果より、このシールドでは、「プリアンプ部から出力されたクロック波形のスレッショルド付近で小さなバタつきがあり、カウンタは1クロックで、2クロック分のカウントしている様です」 とのアドバイスを正に裏付ける結果となりました。

適確なアドバイスを有難うございました。

電子回路は、なかなか奥が深いですね。 今回でまたまた勉強になりました。 工学は失敗から発展してきたとある専門家が言っていましたが、失敗の積み重ねが ノウハウ や ノウホワイ を蓄積して行くことを実感した次第である。 それにしても本格的なオシロが欲しくなりました。 今回のような小さなバタつきも発見出来るような性能のものが欲しいですね。

最後に、影響のなかった実験2の作動確認用のLEDを元に戻しておきました。 そして、その状態での動作確認を実施したことは言うまでもありません。 実験後のシールドと実験中の状態を記録として残しておくことにしましょう。

そして、修正した回路図も記載しておきます。

2016/6/29 作成